# DDR5/LPDDR5 Test Challenges and Insight of Gen 6

Jacky Yu 2021.12

Solutions Engineer / Keysight Technologies

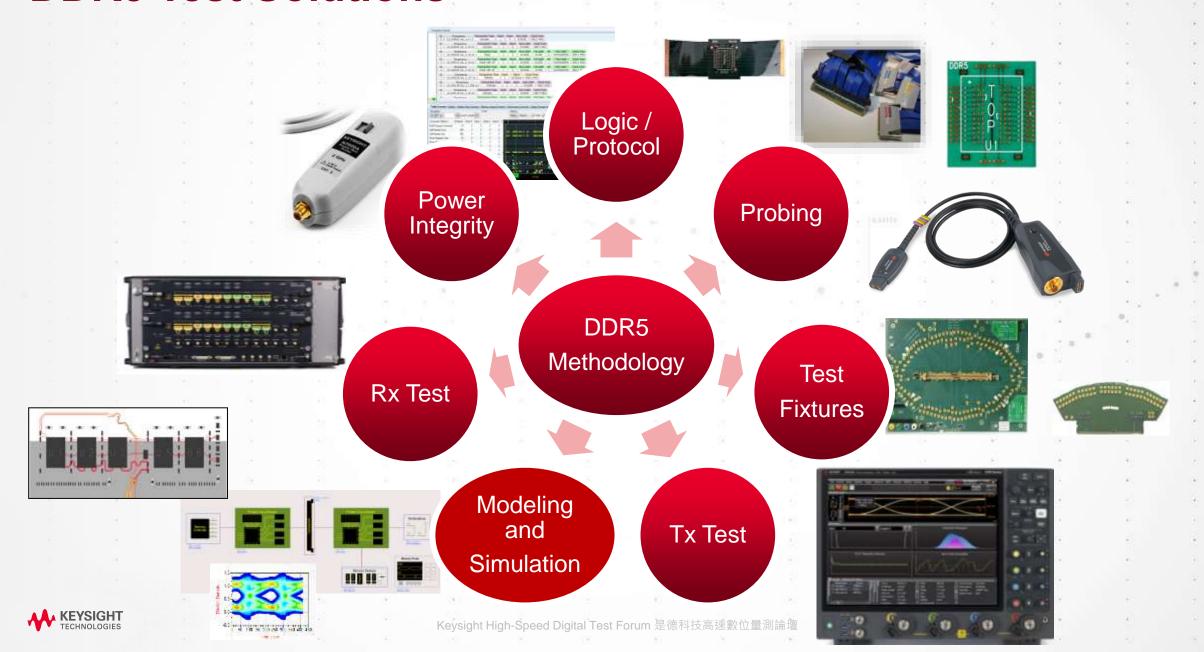

# **DDR5 Test Solutions**

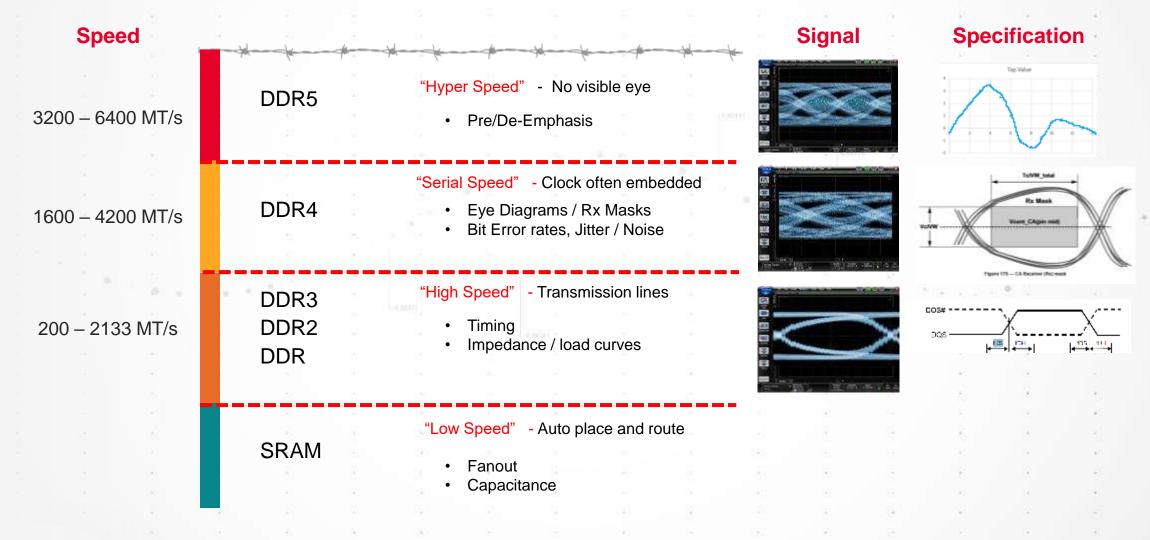

# **DDR Signal Evolution**

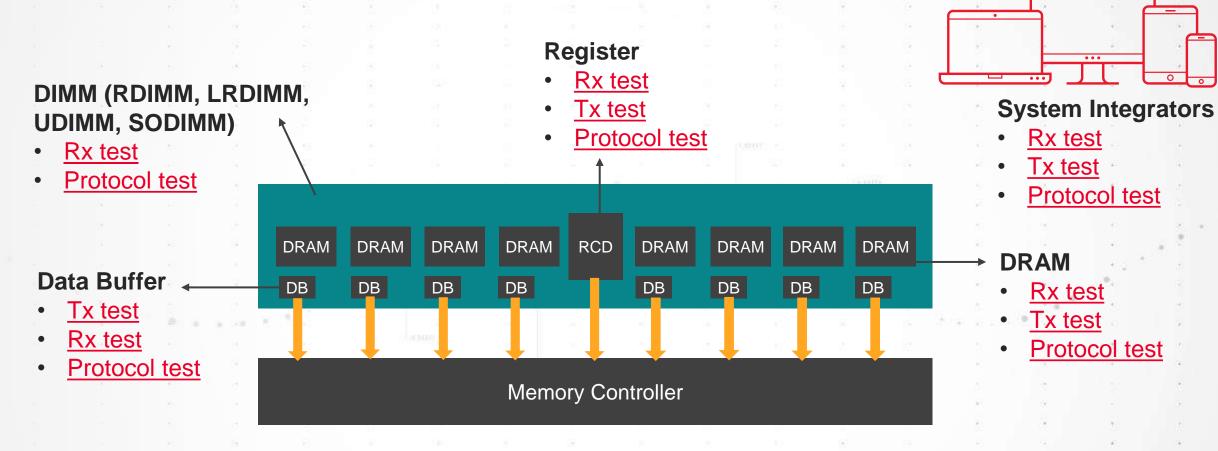

## **DDR5** Devices

# **DDR5 Tx Design Test and Validation**

#### **CHALLENGES AND SOLUTIONS**

#### **CHALLENGES**

Signal integrity

Ensure interoperability

Time-to-market Pressure

#### **SOLUTIONS**

New definition of test parameters

Characterization and compliance test

The total solution approach

**Design and Simulation**

**Analysis and Debug**

Compliance

**Data Analytics**

# **Signal Integrity**

#### **NEW DEFINITION AND SPECIFICATION**

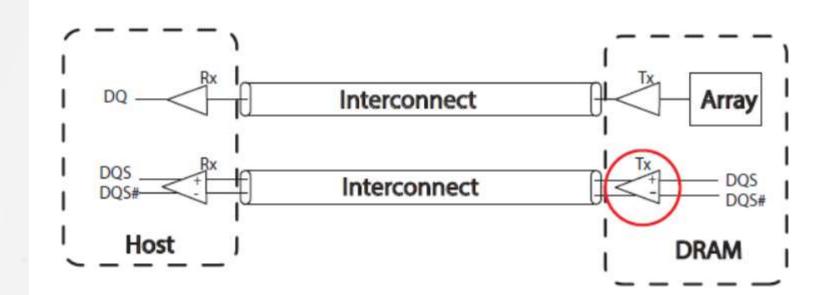

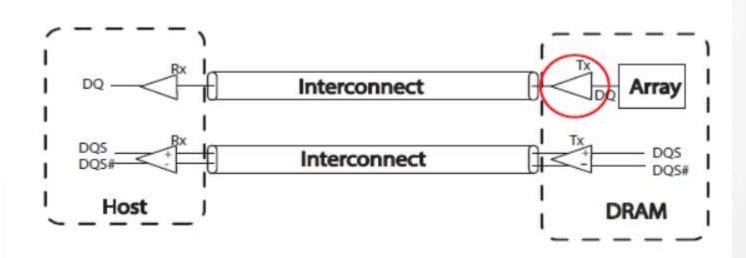

#### New method to perform read and write data separation is required

Legacy method to use DQS-DQ phase difference and pre-amble pattern may no longer be applicable

#### New test parameters are defined to characterize key signals operating at faster data rate

- Specification reveals tighter DQS, DQ, CK nUI jitter tests

- Duty Cycle Adjuster (DCA) optimized jitter measurements

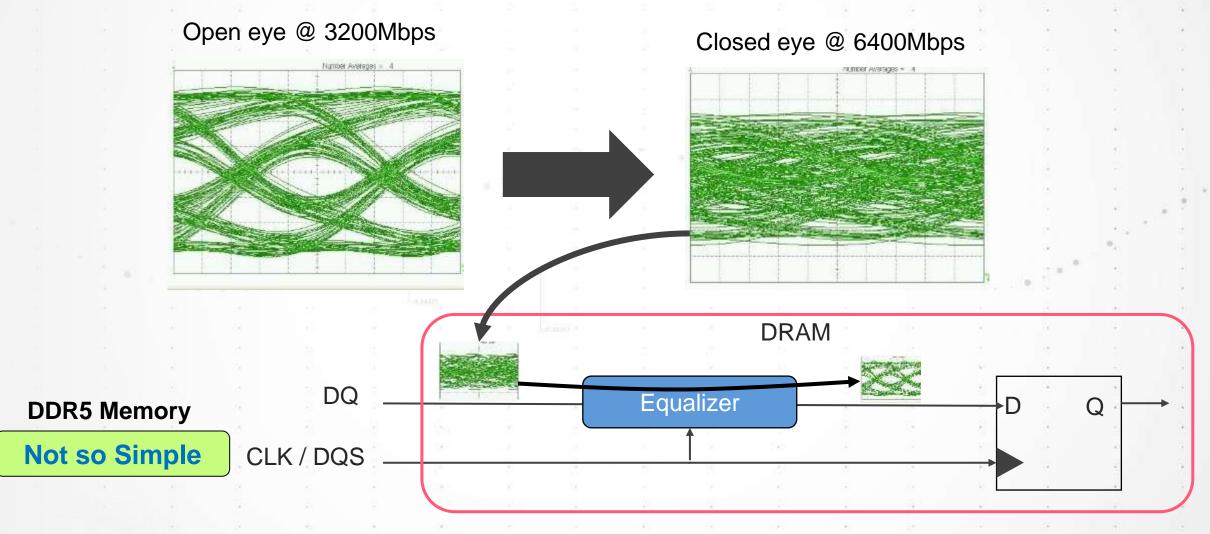

#### Faster data rate may cause data eye to close

- New method to characterize data is required

- Equalization may be required for speed above 3.6 GT/s

# **Ensuring Interoperability**

#### CHARACTERIZATION AND COMPLIANCE TEST

- Best high-performance oscilloscopes

- Complete test coverage:

- Supports the latest DDR5 JEDEC spec

- Speed bin from 3200 to 6400 MT/s

- Supports electrical, timing, jitter and eye diagram tests

- Benefits:

- Ensure interoperability between system and devices

- Repeatability for accurate statistical analysis

- Automation for speedy test time

# Tx - New Specs

- tCK\_NUI jitter (Dj Rj)

- DQS\_NUI jitter (Dj Rj)

- DQ\_NUI jitter (Dj Rj)

- DQ\_Stressed Eye

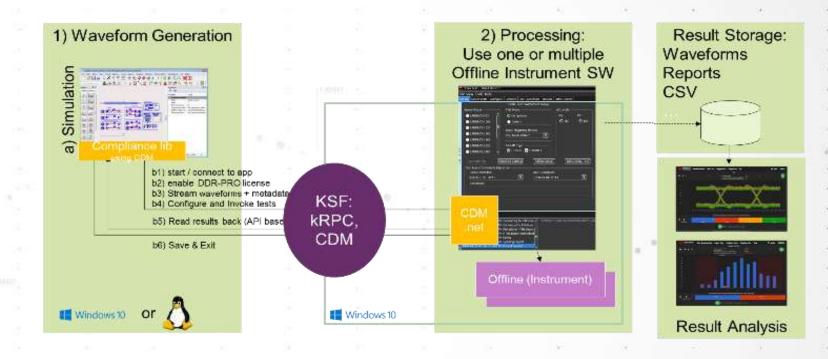

### **Time to Market Pressure**

#### THE TOTAL SOLUTION APPROACH

- Automated Compliance test for speedy test time

- New algorithm for fast test time

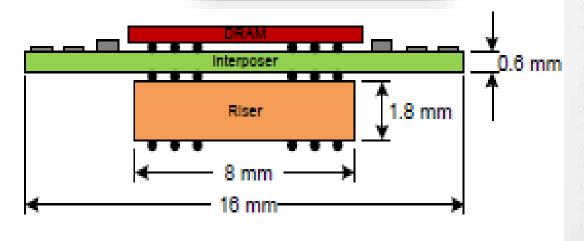

- BGA interposer for easy access to signal for testing

- Integrated Riser and Interposer for better performance

- Easy attachment to DUT

- New ADS framework for completeness of simulation to validation workflow

- Seamless connection to data repository for quick test result analysis and decision making process

**Design and Simulation**

**Analysis and Debug**

Compliance

**Data Analytics**

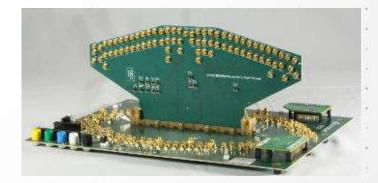

# **Innovative Probing for DDR5**

#### CRITICAL FOR THE TX SOLUTION

- InfiniiMax Ultra Series Probes

- Lowest loading for least impact to your circuit

- Higher density with 1/2 the size of existing solder-in probe heads

- Highest accuracy across the widest frequency range

- DDR5 BGA Interposer

- High performance SI interposer and riser

- New riser designed to minimize crosstalk

- High performance, low loss material

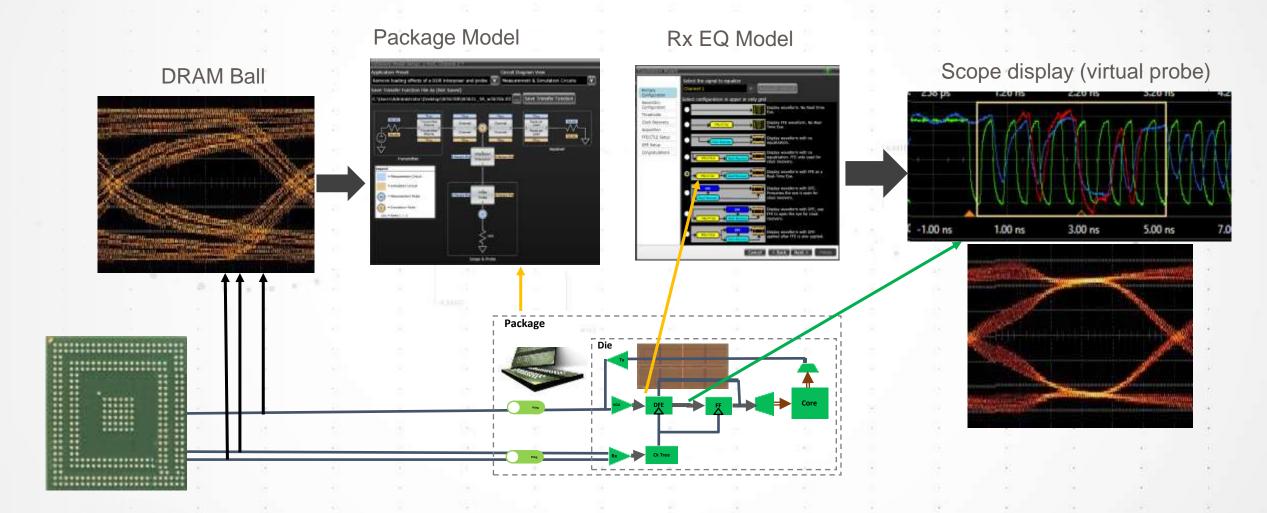

# **DDR5 Tx Test: New Methodology**

#### VIRTUAL PROBING INSIDE THE DIE

# **ADS Integration**

# PATHWAVE

#### INCREASE CONFIDENCE IN THE DESIGN

- Enable better-correlated compliance measurements fewer surprises, shorter time to market.

- Streamlined integration between ADS and Infinitum Offline with DDR5 compliance test app

- ADS automates the configuration and control of the compliance test and receives measurement results back

**Design and Simulation**

**Analysis and Debug**

Compliance

**Data Analytics**

# **Data Analytics**

# PATHW.WE

#### **ENABLE SHORTER TIME TO MARKET**

- Enables:

- Save at least \$1M chip redesign cost

- Increase at least 20% in productivity

- Seamless connection to the KS6810A data analytics software

- Offers enterprise class repository to store the data

- Allows real time data retrieval with modern visualization tool

#### Web server

Hosts KS6810A

Web Service

application

software

#### **Data Import**

Test result with test condition

#### **Data Retrieval**

KS6810A Web Visualization tool

**Design and Simulation**

**Analysis and Debug**

Compliance

**Data Analytics**

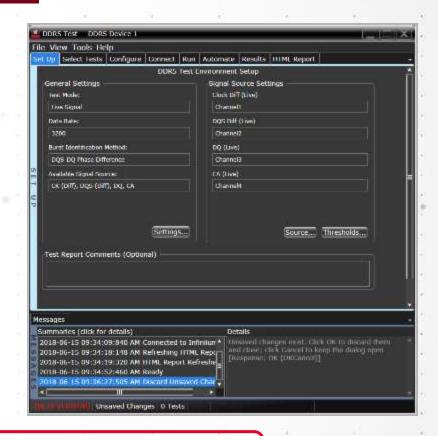

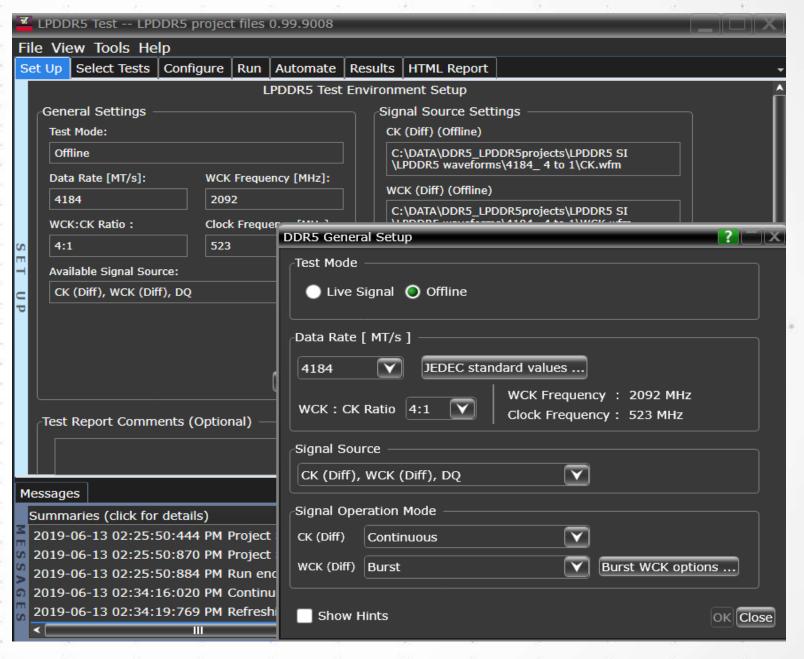

# **Easy Test Setup**

TX SOLUTION

# LPDDR5 application test setup selections:

- Speed grade of device

- Live Signal or Off-line

- Signal sources

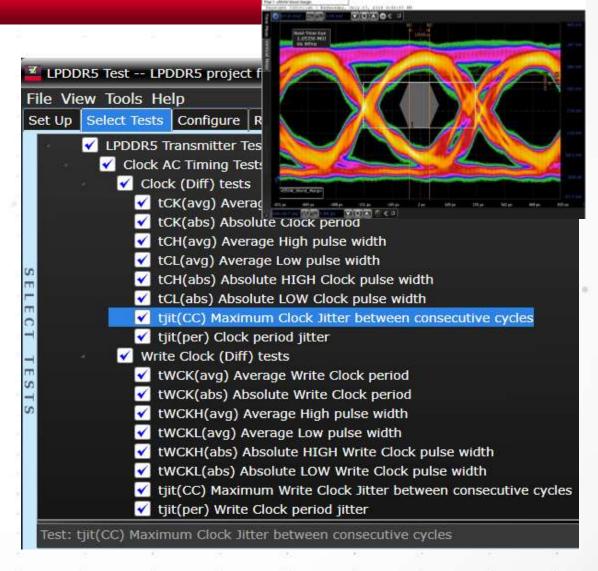

# **Configurability and Guided Connection**

#### TX SOLUTION

- Select Tab lists tests available in the setup.

- Easily setup individual test or groups of tests.

# **Comprehensive Compliance App Format and Features**

#### TX SOLUTION

| Pass | #<br>Failed | #<br>Trials | Test Name                                | Actual Value                | Margin  | Pass Limits                                                            |

|------|-------------|-------------|------------------------------------------|-----------------------------|---------|------------------------------------------------------------------------|

| 1    | 0           | 1           | Vindiff_CK                               | 1.745 V                     | 398.6 % | VALUE >= Vindiff_CK_Limit_Min V                                        |

| 1    | 0           | 1           | Vindiff CK/2HighPulse                    | 894 mV                      | 410.9 % | VALUE >= Vindiff_CK_Limit_Min V                                        |

| 1    | 0           | 1           | Vindiff_CK/2LowPulse                     | 829 mV                      | 373.7 % | VALUE >= Vindiff_CK_Limit_Min V                                        |

| 1    | 0           | 1           | VIHdiff_CK                               | 728 mV                      | 402.1 % | VALUE >= VIHdiff_CK_Limit_Min V                                        |

| 1    | 0           | 1           | VILdiff CK                               | -785 mV                     | 441.4 % | VALUE <= VILdiff_CK_Limit_Max V                                        |

| 1    | 0           | 1.          | SRIdiffR_CK                              | 4.814 V/ns                  | 23.5 %  | SR_Limit_Min V/ns <= VALUE <= SR_Limit_Max V/ns                        |

| 1    | 0           | 1           | SRIdiffF_CK                              | 2.211 V/ns                  | 1.8 %   | SR_Limit_Min V/ns <= VALUE <= SR_Limit_Max<br>V/ns                     |

| 1    | 0           | 1.          | tCK(avg) Average Clock period            | 3.639 ns                    | 0.6 %   | tCK_avg_Limit_Min s <= VALUE <=<br>tCK_avg_Limit_Max s                 |

| 1    |             | 1           | tCK(abs) Absolute Clock period           | 3.017 ns                    |         | Information Only                                                       |

| 1    | 0           | 1           | tCH(abs) Absolute HIGH Clock pulse width | 517.166290123 mtCK (avg)    |         | tCHL_abs_Limit_Min tCK(avg) <= VALUE <= tCHL_abs_Limit_Max tCK(avg)    |

| 1    | 0           | 1           | tCH(avg) Average High pulse width        | 496.692500000 mtCK<br>(avg) | 45.9 %  | tCHL_avg_Limit_Min tCK(avg) <= VALUE <= tCHL_avg_Limit_Max tCK(avg)    |

| ×    | 1           | 1           | tCL(abs) Absolute LOW Clock pulse width  | 338.559219496 mtCK (avg)    | -65.3 % | tCHL_abs_Limit_Min tCK(avg) <= VALUE <=<br>tCHL_abs_Limit_Max tCK(avg) |

#### **Test Report includes:**

- Pass/Fail indicator, # of Trials

- Test Name, Actual value

- Margin

- Pass limits

- Image (where appropriate)

**Summary of Results**

#### **Test Report**

Overall Result: FAIL

| Test C                  | onfiguration Details                |  |  |

|-------------------------|-------------------------------------|--|--|

|                         | Application                         |  |  |

| Name                    | D9050LDOC LPDDR5 Test               |  |  |

| Version                 | 0.99.9035.0                         |  |  |

| De                      | vice Description                    |  |  |

| Test Mode               | Live Signal                         |  |  |

| Data Rate [MT/s]        | 1500                                |  |  |

| WCK:CK ratio            | 2:1                                 |  |  |

| Tes                     | t Session Details                   |  |  |

| Infinitum SW Version    | 64.00.00805                         |  |  |

| Infiniium Model Numbe   | F DSO91304A                         |  |  |

| Infinitum Serial Number | No Serial                           |  |  |

| Debug Mode Used         | No                                  |  |  |

| Compliance Limits       | LPDOR5-800MHz Test Limit (official) |  |  |

| Last Test Date          | 2019-07-17 16:17:02 L/TC +08:00     |  |  |

| Pass | # Faile | d # Trials | Test Name             | Actual Value | Margin | Pass Limits                     |  |

|------|---------|------------|-----------------------|--------------|--------|---------------------------------|--|

| 1    | 0       | 1          | Vindff_CK             | 522 mV       | 49.1 % | VALUE >= Vindiff_CK_Limit_Min V |  |

| 1    | 0       | 1          | Vindit_CK/2High/Pulse | 259 mV       | 48.0 % | VALUE >= Vindif_CK_Limit_Min V  |  |

| 1    | 0       | 1          | Vindift_CK/2LowPulse  | 244 mV       | 39.4 % | VALUE >= Vindiff_CK_Limit_Min V |  |

|      | 0       | 1          | VEHIIIT_OS            | 234 mV       | 61.4 % | VALUE >= VIHdiff_CK_Limit_Min V |  |

| 1    | 0       | 1          | VILdiff_CK            | -204 mV      | 40.7 % | VALUE <= VILdiff_CK_Limit_Max.V |  |

# **DDR5 Rx Design Test and Validation**

#### CHALLENGES AND SOLUTIONS

#### **CHALLENGES**

Signal integrity

Ensure interoperability

Time-to-market Pressure

#### **SOLUTIONS**

New definition of specification

Leadership in measurement methodologies

Test Automation Software

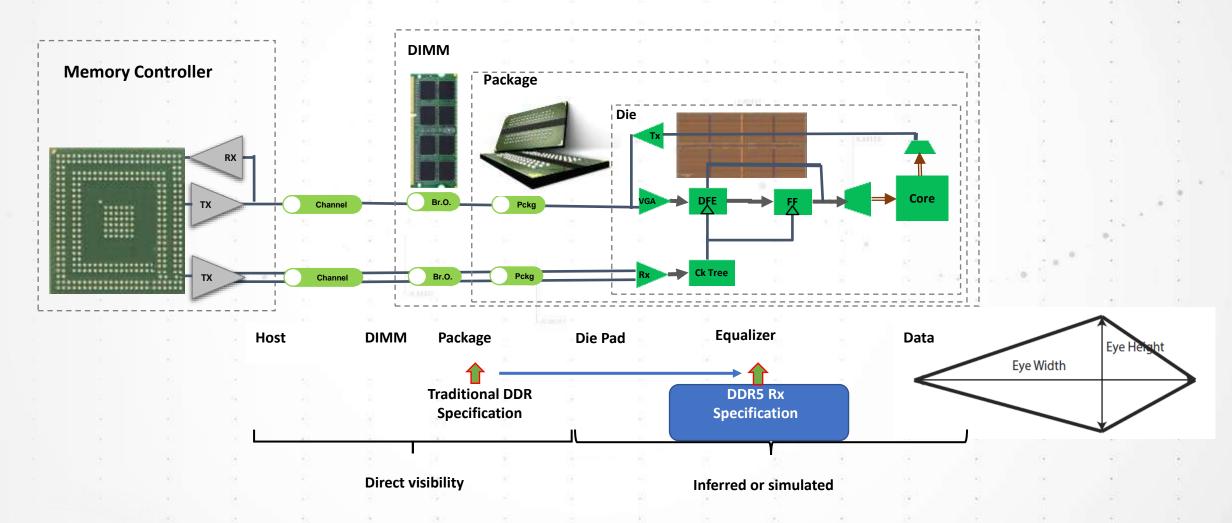

# **DDR Rx Compared to High Speed Serial**

**CDR** Rx data Equalizer Q Implicit clock **High Speed Serial** Multiplying Ref Clk frequency detector (e.g. PLL) Complex (sub-rate) Clock generator Early / late detector **DDR Memory** DQ **Simple** CLK / DQS

# **Shrinking Margins**

#### **NEW RX DEFINITION IN THE SPECIFICATION**

## **Characteristics of DDR5 signals**

- The data signals are wide and single-ended

- Increased emphasis on multi-channel Rx test impairments

- Bidirectional data

- Specification impacts on both write and read training

- DQS (strobe) is bursty instead of a continuous clock

- ISI impact differs on preamble, first bits and the rest of burst

1600 MT/s

3200 MT/s

6400 MT/s

# **DDR5** is a New Game

#### **EQUALIZATION NEEDED TO OPEN EYE**

# **Defining Measurement Requirements**

#### PROVIDE LEADERSHIP IN NEW MEASUREMENTS

- Keysight and early technology adopters are working with the JEDEC standard in defining key Rx specifications

- Keysight is taking the leadership in:

- Measurement requirements to characterize Rx parameters

- Provide hardware and software requirements to enable full Rx testing capabilities

### **Time to Market Pressure**

#### THE TOTAL SOLUTION APPROACH

- New Rx compliance test software

- Amplitude, jitter, crosstalk, stressed eye, DFE calibration tests

- Voltage, jitter sensitivity, and stressed eye tests

- Supports fixtures to complement Rx test requirements

- Channel test card

- Channel modelling board

- Device and Parametric DIMM test card

- Seamless connection to data repository for quick test result analysis and decision making process

## **Test Fixtures**

#### KEY COMPONENTS TO RX TEST

#### Channel Test Card - CTC2

- Socket for plugging in DIMM test card for calibration, DIMM module to be tested, or device test board

- SMP connectors to provide access to CA/CTRL, strobe, and data

#### ISI board

Contains different length standard compliant channels

#### Device Test Card

Plugs into CTC and can be used by memory/register manufacturers to test their chips

#### Fully Passive DIMM Test Card

- Plugs into CTC

- Signal breakout board for clock, CA, CTRL, strobe, and data

- Used for signal inspection and Rx stress signal calibration

- Signals are routed to SMP connectors

CTC2

**DIMM Test Card**

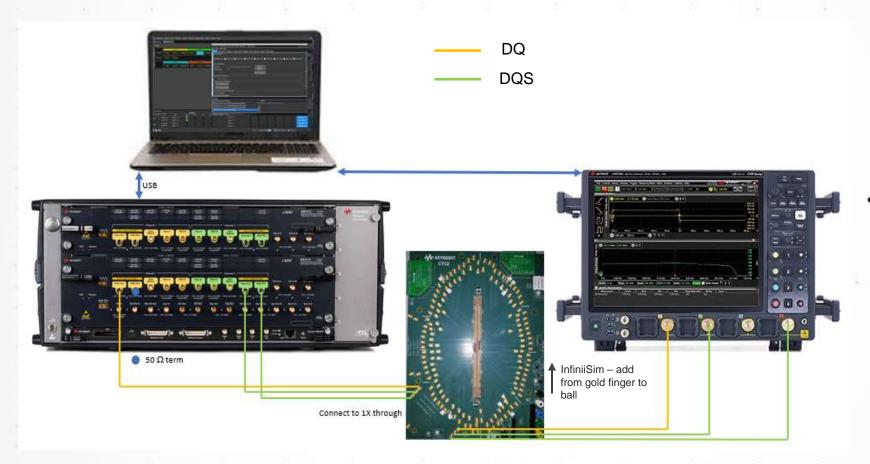

# **Calibration Connection Diagram - RDIMM**

Scope is a reference receiver

InfiniiSim – remove cable between 1X and scope

# Test and Characterization Diagram (DQS/DQ)

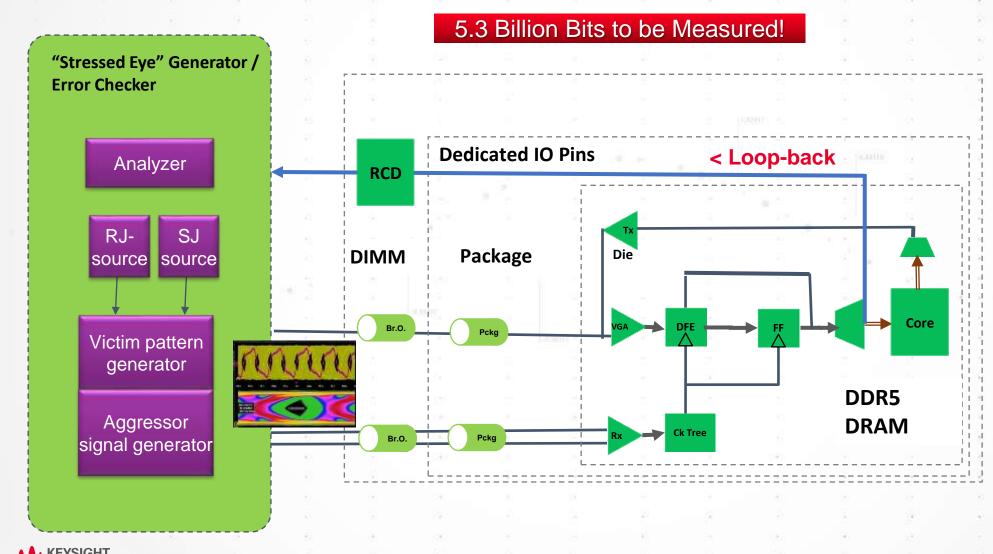

# DDR5 Rx Specifications are now Inside the Die

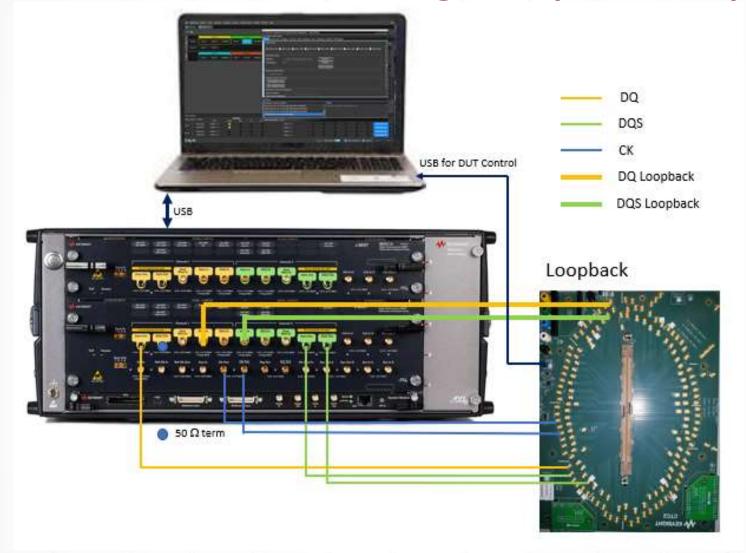

# Accurate DDR5 Rx Specifications via Loop-Back Mode

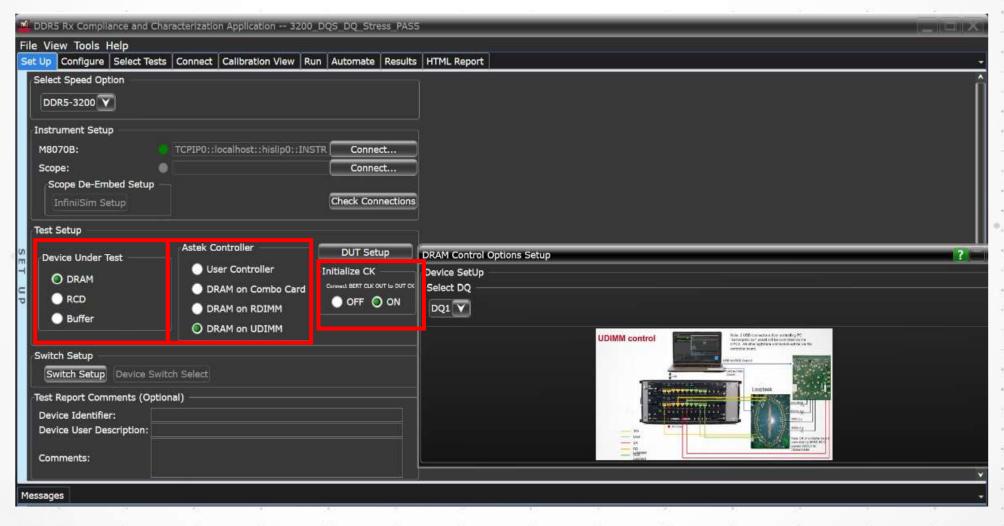

# DDR5 RX M80555RCA Calibration/Testing software

M80885A GUI

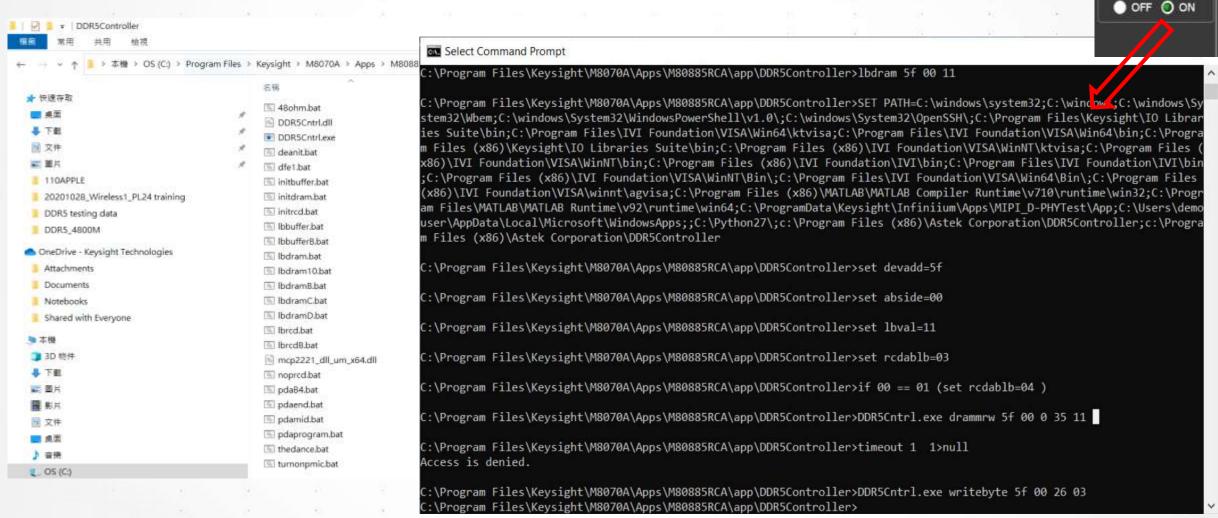

# DDR5 RX DUT initializing/Loopback CML

#### Initialize CK to make DUT initializing

**DUT Setup**

Consect BERT CLK OUT to DUT CK

Initialize CK

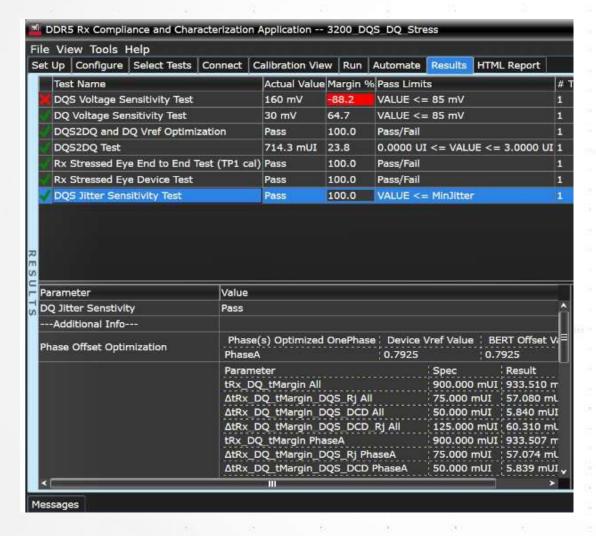

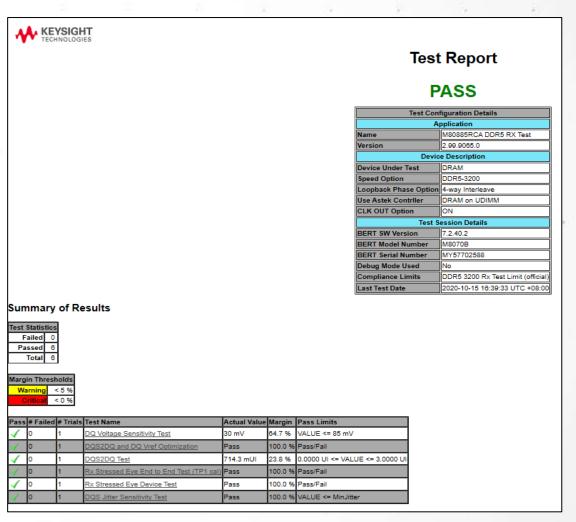

# **DDR5 3200M RX Testing Report**

#### **Keysight Standard Report**

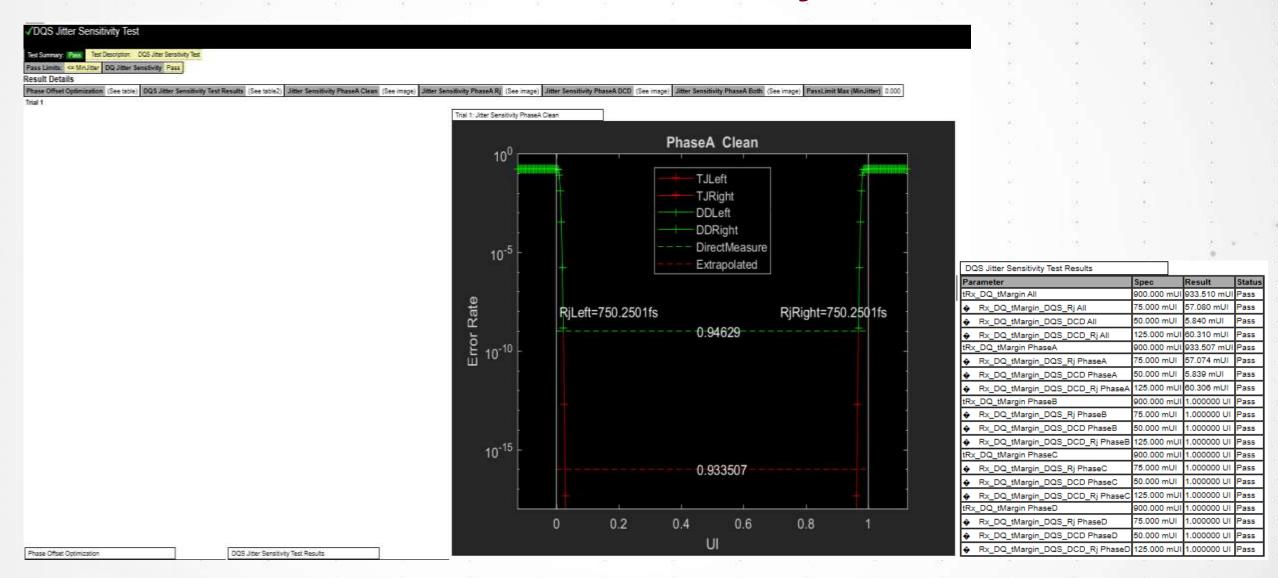

# **DDR5 3200M RX DQS Jitter Sensitivity**

# **DDR5 and LPDDR5 Probing Challenges and Solutions**

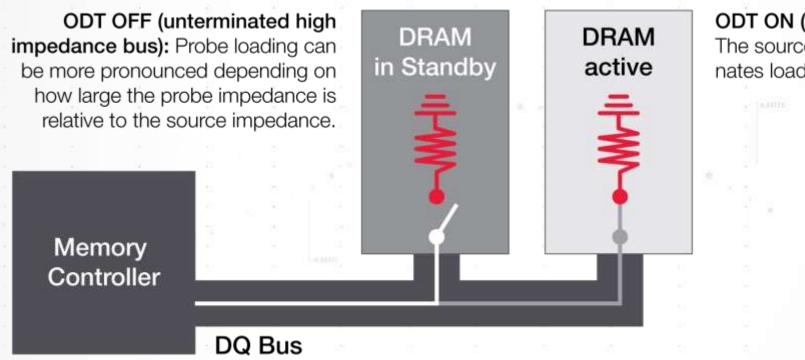

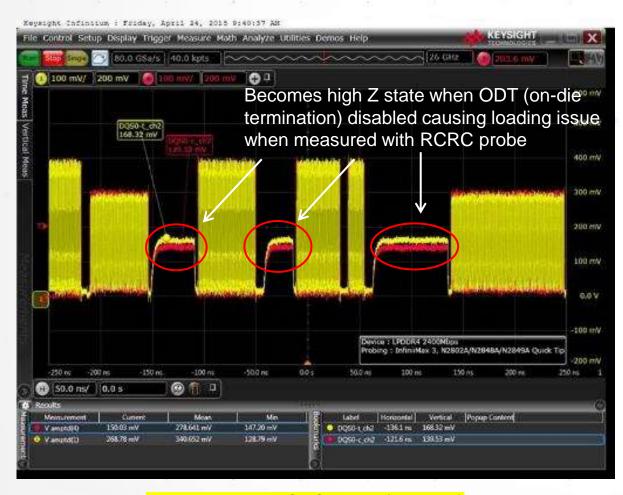

# **DDR Memory On-die Termination Modes**

#### PROBE INPUT IMPEDANCE RELATIVE TO SOURCE

#### ODT ON (low impedance bus):

The source impedance dominates loading.

Dynamic ODT enables the DRAM to switch between high or low termination impedance. When the termination impedance goes high, probe impedance needs to be high enough to reduce probe loading.

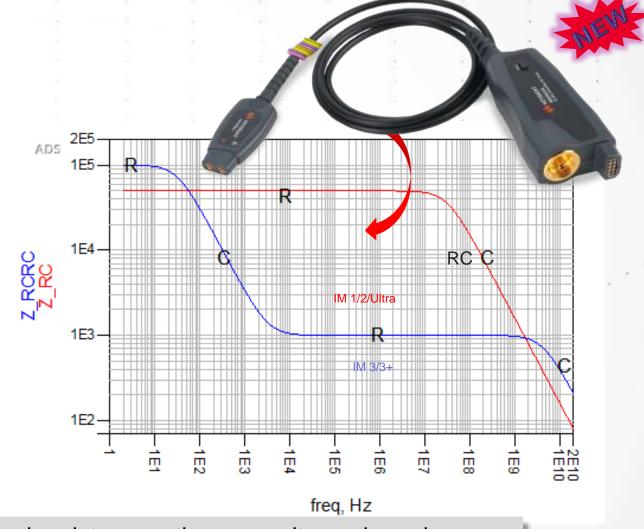

# Ultra InfiniiMax 25 GHz RC Probe Overview

- 25 GHz (with MX0100A micro head)

- AutoProbe II interface direct plug-in to UXR Jr, V, Q, 90kX

- RC input impedance profile with low midband loading

- 25 k ohm input R @DC each signal to ground

- 0.17 pF input C when used with MX0100A

- Compatible with most of InfiniiMax I/II probe head accessories

"RC" (red trace): traditional resistance – then capacitance impedance "RCRC" (blue trace): High DC impedance, moderate mid-band

# RC vs RCRC Probe For Probing LPDDR4 Signal

RC probe is a better choice when probing buses that transition to a "high Z" state or when dealing with signal with high impedance.

Measured with RC probe (1169B)

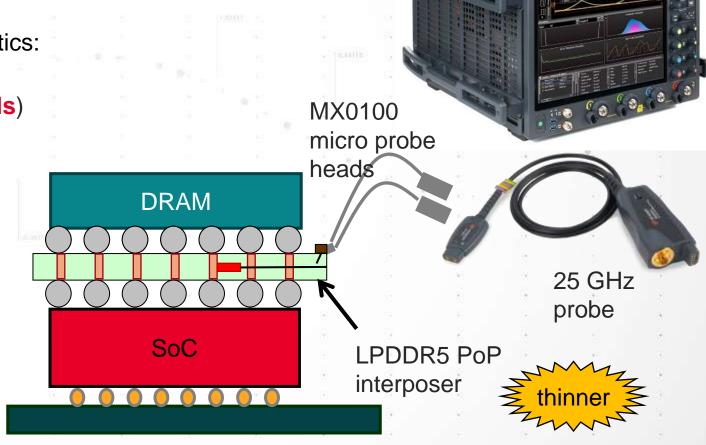

## **New PoP/BGA Interposers for DDR5 and LPDDR5**

#### CRITICAL FOR TX AND PROTOCOL SOLUTIONS

**UXR** scope

- Previous generation BGA/PoP interposer design/materials don't cover DDR5/LPDDR5 data rates.

- New BGA/PoP interposer designs characteristics:

- Thinner (previously 70 mils, new 20 22 mils)

- New materials and processes.

- Improved SI

- Decreased crosstalk

- Integrated Riser + Interposer

- Better performance than separate parts

- Easier attachment to DUT

- Available on custom probes

# **DDR5 Protocol Design Test and Validation**

#### CHALLENGES AND SOLUTIONS\*

#### **CHALLENGES**

Ensure interoperability

Identify root cause of system failure

#### **SOLUTIONS**

Protocol Compliance and validation

Debug with complete view of the DDR traffic using powerful analysis tools

Time-to-market Pressure

\* DDR5 data rate coverage will vary by system under test and logic analysis solution.

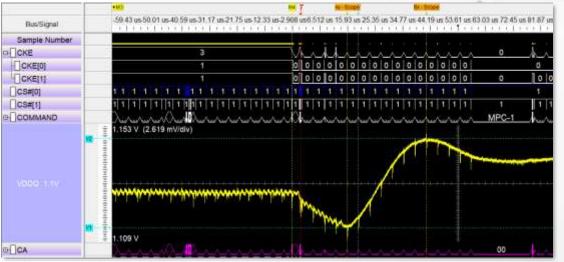

Viewscope to visualize noise on power or signal integrity issues correlated to memory analysis

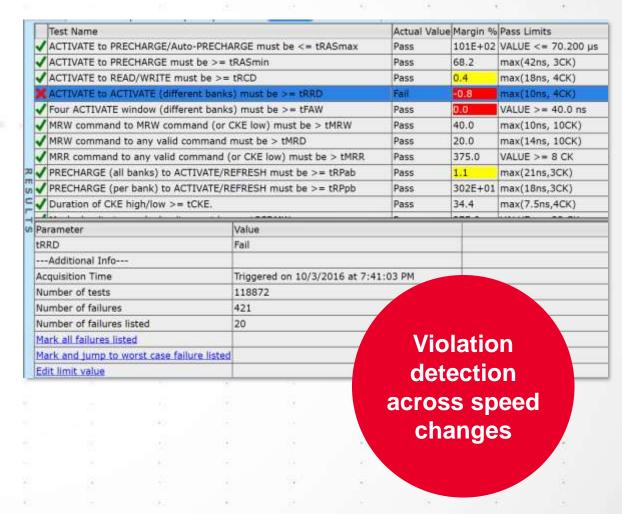

# **Ensure Interoperability**

#### PROTOCOL COMPLIANCE AND DATA VALIDATION

#### **Test**

Test and monitor your system under variable conditions

#### **Functional Compliance Validation**

- Validate system is within JEDEC specifications

- Quick pass/fail results

- Includes margin information on how far the system is deviating from the 'pass limits'

- Includes number of times violation occurred and how many times violation was tested

- If not.....risk of system failures

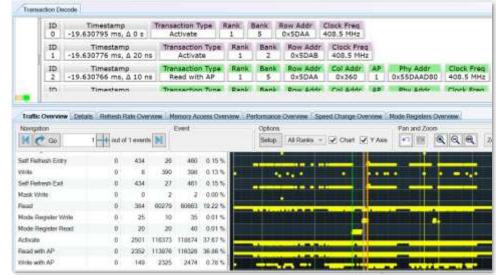

# **Identify Root Cause of System Failure**

#### **DEBUG CAPABILITIES**

#### Something is wrong with your system

- Check the flow of the traffic between the memory controller and memory device to get to the root cause of system issues

- Correlate memory traffic to scope capture of:

- Signal integrity of specific signals

- Power integrity

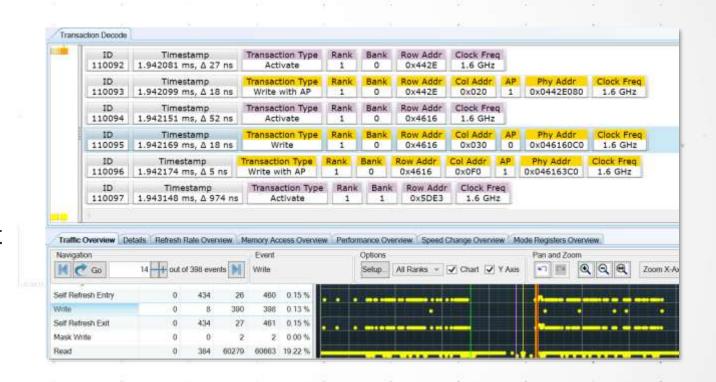

#### **Time to Market Pressure**

#### ANALYSIS SW TOOLS ACCELERATE INSIGHT

- Rapid Navigation with Traffic Overview, Transaction Decode, Details tab, Refresh Overview, Memory Access Overview, Performance Overview, Mode Register Overview, and Speed Change Overview

- See when events happened

- Follow signal flow and understand, "What happened?"

- Compliance testing to locate potential failures

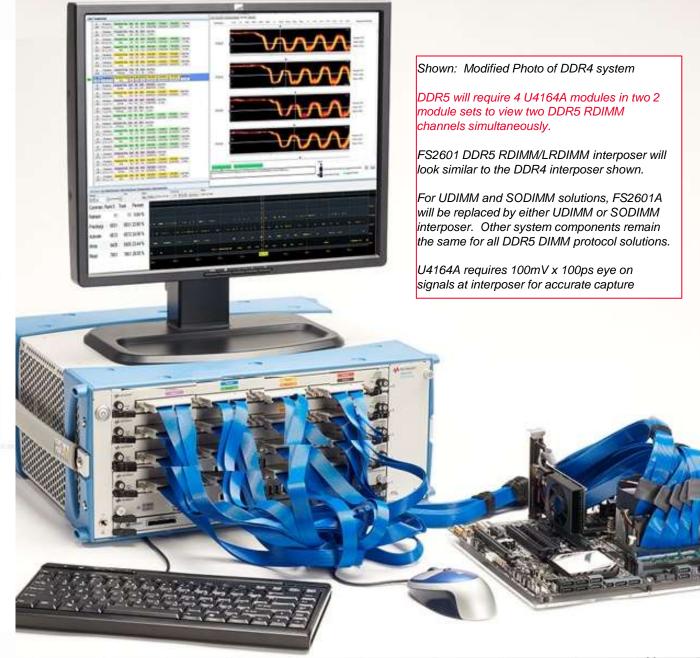

# DDR5 configuration for RDIMM or LRDIMM

- Qty (4) U4164A logic analyzer modules qty (2) sets of 2 modules

- Qty (4) option -02G speed grade option

- Qty (4) optional customer choice of memory depth options

- Qty (1) M9505A chassis

- Qty (1) M9537A embedded controller

- Qty (1) FS2600 or FS2604 DDR5 RDIMM/LRDIMM Interposer

- Qty (1) B4661A Memory Analysis SW

- Qty (1) B4661A-5FP/5TP/5NP DDR5 Analysis and Compliance Validation

# Looking Ahead – DDR6\*

- DDR5 started in 2016

- Typical 5 year spec development process

- Expect DDR6 spec development late 2022, early 2023

- Keysight DDR6 pathfinding

- Crosstalk more focus

- Fully closed eye specification

- Double bandwidth with similar power budget

- Low noise UXR oscilloscope to meet jitter/eye limits

- M8040A BERT for NRZ/PAM4 signaling support

|                 | DDR5     | DDR6*     |

|-----------------|----------|-----------|

| Capacity        | 8 GB     | 16 GB     |

| Burst<br>length | 16       | 32        |

| Max speed       | 8.4 GT/s | 16.8 GT/s |

<sup>\*</sup> Keysight opinion, not official JEDEC specs or plans. Based on historical 2x performance improvements over similar channels